DHCOM iMX6ULL-D2: Difference between revisions

From Wiki-DB

Jump to navigationJump to search

| Line 67: | Line 67: | ||

==== U-Boot (for eMMC COMs) ==== | ==== U-Boot (for eMMC COMs) ==== | ||

* [[media:U-boot-with-spl_imx6ull_2018.05-DH_v0.23_emmc-g3976eca016.imx|DH U-Boot v0.23 (based on v2018.05)]] | * [[media:U-boot-with-spl_imx6ull_2018.05-DH_v0.23_emmc-g3976eca016.imx|DH U-Boot v0.23 (based on v2018.05)]] | ||

: [[DHCOM Update Mechanism#Commandline Mode| | : [[DHCOM Update Mechanism#Commandline Mode|More on how to program it on page "DHCOM Update Mechanism"]] | ||

==== Update Kernel ==== | ==== Update Kernel ==== | ||

* [[media:2020-02-10_imx6ull_updatekernel.zip|Update Kernel Release 2020-02-10]] | * [[media:2020-02-10_imx6ull_updatekernel.zip|Update Kernel Release 2020-02-10]] | ||

: [[DHCOM Update Mechanism|More on how to use it on page "DHCOM Update Mechanism"]] | |||

==== Debian based images ==== | ==== Debian based images ==== | ||

Revision as of 14:08, 3 March 2020

|

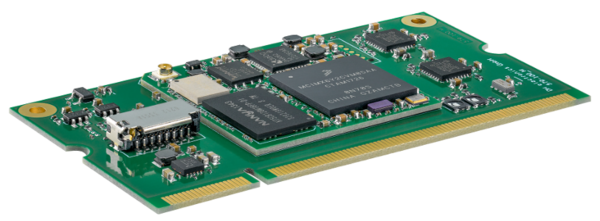

Hardware

|

|

Software Support

BSP Sources

- Mainline

Download binaries/images

U-Boot (for eMMC COMs)

Update Kernel

Debian based images

- Debian 8 "Jessie" + Kernel 4.19.25 Release 2020-03-03