Avenger96: Difference between revisions

From Wiki-DB

Jump to navigationJump to search

Ageisreiter (talk | contribs) |

Ageisreiter (talk | contribs) |

||

| Line 28: | Line 28: | ||

**1x ARM® Cortex-M4 up to 200 MHz | **1x ARM® Cortex-M4 up to 200 MHz | ||

''' | ''' | ||

* | *'''GPU''' 1x 3D GPU Vivante® @ 533 MHz - OpenGL® ES 2.0 | ||

*'''PMIC''' STPMIC1A | |||

* | *'''DDR3 DRAM''' 1024 Mbyte @ 533 MHz | ||

* | *'''eMMC Flash''' 8 Gbyte, v4.51 interface | ||

* | *'''NOR Flash''' 2 Mbyte, Quad SPI interface | ||

* | *'''EEPROM''' 128 byte | ||

* | *'''microSD Socket''' UHS-I speed grade, v3.01 | ||

* | *'''USB Host''' 2x type A, 2.0 high-speed | ||

* | *'''USB OTG''' 1x type micro-AB, 2.0 high-speed | ||

*'''HDMI''' WXGA (1366x768) @ 60 fps, HDMI 1.4 | |||

*'''WiFi / Bluetooth''' | |||

* USB 2.0 | **WiFi 5 GHz & 2.4GHz IEEE 802.11a / b / g / n / ac | ||

* | **Bluetooth® v4.2 (BR/EDR/BLE) | ||

* | **PCB antenna | ||

* | *'''Ethernet''' 10 / 100 / 1000 Mbit/s, IEEE 802.3-compliant | ||

|valign="top" style="border: 0pt;" | | |valign="top" style="border: 0pt;" | | ||

* | *'''Push-Buttons''' Power and reset | ||

*'''Battery Socket''' CR1216, CR1220 and CR1225 | |||

*'''''' | |||

* | *'''''' | ||

* | *'''''' | ||

* | *'''''' | ||

* | *'''''' | ||

* | *'''''' | ||

* | *'''''' | ||

* | *'''''' | ||

* | *'''''' | ||

* | |||

* | |||

|} | |} | ||

Revision as of 13:07, 21 February 2019

|

Introduction

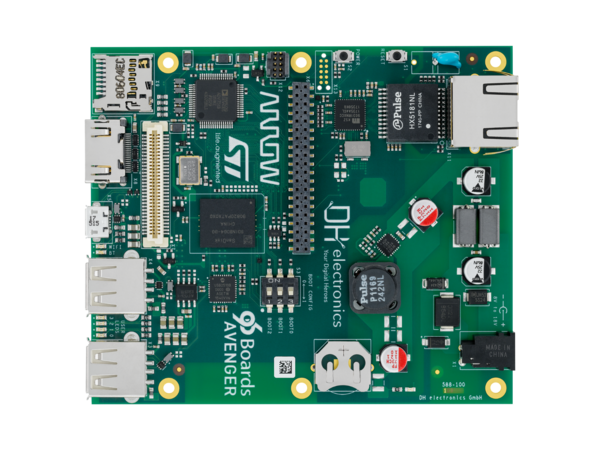

The AVENGER Board is a 96Boards compliant consumer edition board based on the STM32MP15 series of SoCs. The STM32MP15 series is a highly integrated multi-market applications processor designed to enable secure and portable applications within the Internet of Things. AVENGER board features Dual-core Arm® Cortex®-A7 processors operating at up to 650 Hz, Single core Arm® Cortex® M4 operating up to 200 MHz. In addition, an extensive set of interfaces and connectivity peripherals are included to interface to cameras, touch-screen displays, MMC/SD cards and media processor engine. It also fully supports wireless communication, including WLAN and BLE.

Hardware

|

|