DHCOM iMX6-D2: Difference between revisions

From Wiki-DB

Jump to navigationJump to search

| Line 77: | Line 77: | ||

* [https://www.dropbox.com/s/jw823q3ot4iim06/u-boot-with-spl_imx6_v2.0.8.0_emmc.imx?raw=1 DH U-Boot v2.0.8.0 (based on v2018.05)] | * [https://www.dropbox.com/s/jw823q3ot4iim06/u-boot-with-spl_imx6_v2.0.8.0_emmc.imx?raw=1 DH U-Boot v2.0.8.0 (based on v2018.05)] | ||

* [https://www.dropbox.com/s/qagp43dfd6mjklm/v1-1-0-7_u-boot-imx6qdl.tar.xz?raw=1 DH U-Boot v1.1.0.7 (based on v2015.10)] | * [https://www.dropbox.com/s/qagp43dfd6mjklm/v1-1-0-7_u-boot-imx6qdl.tar.xz?raw=1 DH U-Boot v1.1.0.7 (based on v2015.10)] | ||

: [[DHCOM Update Mechanism#Commandline Mode| | : [[DHCOM Update Mechanism#Commandline Mode|More on how to program it on page "DHCOM Update Mechanism"]] | ||

==== Update Kernel ==== | ==== Update Kernel ==== | ||

* [https://www.dropbox.com/s/x46x2u2081fwln3/2018-02-01_imx6_updatekernel.zip?raw=1 Update Kernel Release 2018-02-01] | * [https://www.dropbox.com/s/x46x2u2081fwln3/2018-02-01_imx6_updatekernel.zip?raw=1 Update Kernel Release 2018-02-01] | ||

: [[DHCOM Update Mechanism|More on how to use it on page "DHCOM Update Mechanism"]] | |||

==== Debian based images ==== | ==== Debian based images ==== | ||

Revision as of 12:08, 3 March 2020

|

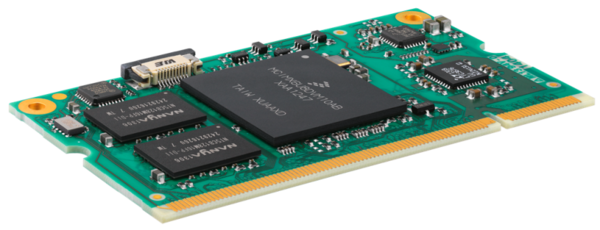

Hardware

|

|

Software Support

BSP Sources

U-Boot

Linux Kernel

- Mainline

- NXP Vendor

Download binaries/images

U-Boot (for eMMC COMs)

Update Kernel

Debian based images

- Debian 8 "Jessie" + Kernel 4.4.60 Release 2017-05-29

- Debian 8 "Jessie" with Qt5.9.1 + Vendor Kernel 4.1.15 Release 2017-10-06

Download Linux code examples

Code Examples for Userspace-Applications to Access SPI, I2C, GPIOs, and more

Download WEC

WEC7 DHHalLib.dll (function library)

- Download DHHalLib Library Version 1.3.0.0

- DHHalLib Demo App Source Code

- DHHalLib Demo App Binary File

- Download DHHalLib CSharp Demo Wrapper App

- Download DHHalLib CSharp Demo Wrapper App Binary File