DHCOM Settings: Difference between revisions

From Wiki-DB

Jump to navigationJump to search

No edit summary |

No edit summary |

||

| Line 1: | Line 1: | ||

__toc__ | __toc__ | ||

The Hardware settings | The Hardware settings can be configured by the DHCOM settings file in flash memory. The file contains the following settings: | ||

:[[Image:DHCOM Settings Block.png|1000px]] | :[[Image:DHCOM Settings Block.png|1000px]] | ||

| Line 53: | Line 53: | ||

| HW_CONFIG_FLAGS || Hardware Configuration Register || see description | | HW_CONFIG_FLAGS || Hardware Configuration Register || see description | ||

|} | |} | ||

: | ==='' Remark: How to choose a PIXEL_CLOCK: ''=== | ||

===='' DHCOM iMX25 ''==== | |||

The frequency of the clock-source for the pixel clock is 66.500 MHz. The divider has to be greater or equal 2. Only the following pixel clock frequencies are possible: | |||

:*33.250MHz | :*33.250MHz | ||

:*22.167MHz | :*22.167MHz | ||

| Line 64: | Line 68: | ||

:*6.650MHz | :*6.650MHz | ||

:*... | :*... | ||

=== LCD_CONFIG_FLAGS description: | '''Be aware of the fact if you choose a pixel-clock between two possible values the smaller value will be used.''' | ||

===='' DHCOM AM35 ''==== | |||

The clock-source of the pixel-clock runs with 432 MHz. | |||

== LCD_CONFIG_FLAGS description: == | |||

{|class="wikitable" | {|class="wikitable" | ||

|- | |- | ||

| Line 88: | Line 96: | ||

|} | |} | ||

== GPIO_DIR description: == | |||

{|class="wikitable" | {|class="wikitable" | ||

|- | |- | ||

| Line 103: | Line 111: | ||

|} | |} | ||

== GPIO_STATE description: == | |||

{|class="wikitable" | {|class="wikitable" | ||

|- | |- | ||

| Line 118: | Line 126: | ||

|} | |} | ||

== HW_CONFIG_FLAGS description: == | |||

{|class="wikitable" | {|class="wikitable" | ||

|- | |- | ||

Revision as of 14:59, 8 May 2012

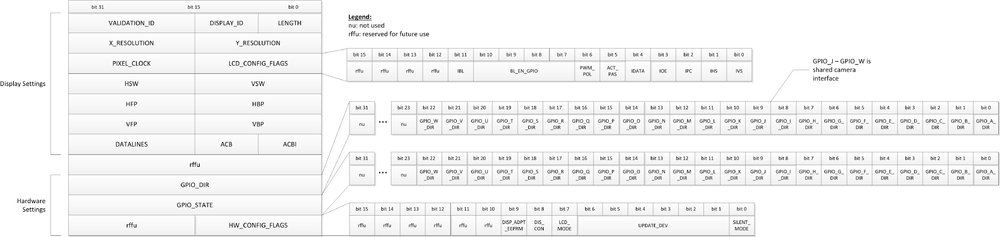

The Hardware settings can be configured by the DHCOM settings file in flash memory. The file contains the following settings:

Supported by

- U-Boot DH VERSION v1.11.0.1 or higher for iMX25

- U-Boot DH VERSION v0.7.0.0 or higher for AM35x

Settings Block description:

| Settings Name: | Description: | Unit: |

|---|---|---|

| VALIDATION_ID | „DH“ | |

| DISPLAY_ID | unique ID of Display | |

| LENGTH | Length of the settings block | |

| X_RESOLUTION | Display x resolution | pixel |

| Y_RESOLUTION | Display y resolution | pixel |

| PIXEL_CLOCK | Pixel clock | kHz |

| LCD_CONFIG_FLAGS | LCD Configuration Register | see description |

| HSW | Horizontal synchronization pulse width | pixel clocks |

| VSW | Vertical synchronisation pulse width | line clocks |

| HFP | Horizontal front porch | pixel clocks |

| HBP | Horizontal back porch | pixel clocks |

| VFP | Vertical front porch | line clocks |

| VBP | Vertical back porch | line clocks |

| DATALINES | count of datalines | number of datalines |

| ACB | AC Bias frequency | |

| ACBI | AC Bias transitions per interrupt | |

| GPIO_DIR | DHCOM GPIO default direction register | see description |

| GPIO_STATE | DHCOM GPIO default state register | see description |

| HW_CONFIG_FLAGS | Hardware Configuration Register | see description |

Remark: How to choose a PIXEL_CLOCK:

DHCOM iMX25

The frequency of the clock-source for the pixel clock is 66.500 MHz. The divider has to be greater or equal 2. Only the following pixel clock frequencies are possible:

- 33.250MHz

- 22.167MHz

- 16.625MHz

- 13.300MHz

- 11.083MHz

- 9.500MHz

- 8.312MHz

- 7.389MHz

- 6.650MHz

- ...

Be aware of the fact if you choose a pixel-clock between two possible values the smaller value will be used.

DHCOM AM35

The clock-source of the pixel-clock runs with 432 MHz.

LCD_CONFIG_FLAGS description:

| Settings Name: | Description: | Unit: |

|---|---|---|

| IVS | Inverted Vertical Sync Pulse | 0 active high / 1 active low |

| IHS | Inverted Horizontal Sync | 0 active high / 1 active low |

| IPC | Inverted Pixel Clock | 0 Data is sampled on rising edge / 1 Data is sampled on falling edge |

| IOE | Inverted Output Enable | 0 active high / 1 active low |

| IDATA | Inverted Data | 0 active high / 1 active low |

| ACT_PAS | Active or passiv matrix display | 0 passiv / 1active |

| PWM_POL | PWM polarity | 0 low state backlight off and high state backlight on / 1 low state backlight on and high state backlight off |

| BL_EN_GPIO | Backlight enable GPIO number | 0 no backlight enable GPIO / 1 DHCOM GPIO_A / 2 DHCOM GPIO_B / … / 9 = DHCOM GPIO_I |

| IBL | Inverted Backlight Enable | 0 active high / 1 active low |

GPIO_DIR description:

| Settings Name: | Description: | Unit: |

|---|---|---|

| GPIO_A_DIR | DHCOM GPIO_A direction | 1 input / 0 output |

| GPIO_B_DIR | DHCOM GPIO_B direction | 1 input / 0 output |

| … | ||

| GPIO_I_DIR | DHCOM GPIO_I direction | 1 input / 0 output |

GPIO_STATE description:

| Settings Name: | Description: | Unit: |

|---|---|---|

| GPIO_A_STATE | DHCOM GPIO_A default state if dir = output | 1 high / 0 low |

| GPIO_B_STATE | DHCOM GPIO_B default state if dir = output | 1 high / 0 low |

| … | ||

| GPIO_I_STATE | DHCOM GPIO_I default state if dir = output | 1 high / 0 low |

HW_CONFIG_FLAGS description:

| Settings Name: | Description: | Unit: |

|---|---|---|

| SILENT_MODE | Disable Bootloader messages on FFUART | 0 enabled FFUART outputs / 1 disabled FFUART outputs |

| UPDATE_DEV | Configures auto update storage devices | 0b000000 All Update Medias disabled

0bxxxxx1 Update via MicroSD Slot 0bxxxx1x Update via SD/MMC Slot 0bxxx1xx Update via USB Host 1 0bxx1xxx Update via USB OTG 0bx1xxxx Update via USB Host 2 0b1xxxxx Update via Ethernet |

| LCD_MODE | Enable Bootloader messages on LCD Display | 1 enabled / 1 disabled |

| DIS_CON | Disable Bootloader console on FFUART | 0 console enabled / 1 console disabled |