DHCOM iMX6ULL-D2: Difference between revisions

From Wiki-DB

Jump to navigationJump to search

No edit summary |

|||

| Line 54: | Line 54: | ||

*[[DHCOM Update Mechanism|DHCOM Update Mechanism]] | *[[DHCOM Update Mechanism|DHCOM Update Mechanism]] | ||

*[[Yocto | Yocto on DHCOM]] | *[[Yocto | Yocto on DHCOM]] | ||

== BSP Sources== | |||

==== U-Boot ==== | |||

* [https://github.com/dh-electronics/u-boot-imx6qdl/tree/dev/legacy/2018.05_dhcom DH U-Boot (based on v2018.05)] | |||

* [https://github.com/dh-electronics/u-boot-imx6qdl/tree/dev/2015.10_dhcom DH U-Boot (based on v2015.10)] | |||

* [https://github.com/dh-electronics/u-boot-imx6qdl/tree/dev/2013.10_dhcom DH U-Boot (based on v2013.10)] | |||

==== Linux Kernel ==== | |||

* Mainline | |||

:* [https://github.com/dh-electronics/linux-imx6qdl/tree/dev/4.4.60_dhcom DH 4.4.60 Development] | |||

:* [https://github.com/dh-electronics/linux-imx6qdl/tree/release/4.4.60_dhcom/20190926 DH 4.4.60 Release 2019-09-26] | |||

:* [https://github.com/dh-electronics/linux-imx6qdl/tree/dev/3.14.12_dhcom DH 3.14.12 Development] | |||

* NXP Vendor | |||

:* [https://github.com/dh-electronics/linux-imx6-vendor/tree/release/v4.1.15/20190624 DH 4.1.15 Release 2019-06-24] | |||

:* [https://github.com/dh-electronics/linux-imx6-vendor/tree/release/v3.10.17/20170804 DH 3.10.17 Release 2017-08-04] | |||

== Downloads == | == Downloads == | ||

Revision as of 14:46, 24 February 2020

|

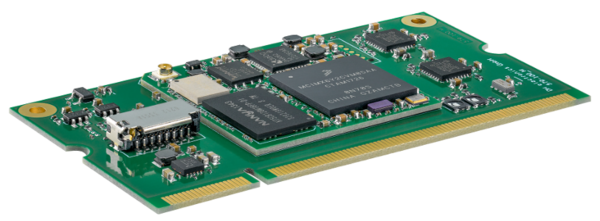

Hardware

|

|

Software Support

BSP Sources

U-Boot

Linux Kernel

- Mainline

- NXP Vendor

Downloads

U-Boot Sources

Update-Kernel

Linux Kernel Sources / Prebuilt Kernels

- Mainline

- Vendor

Debian based root file systems

- Debian alone

- Based on Debian 6 "Squeeze" (2014-10-30)

Remark: Shellshock (CVE-2014-6271) is already fixed.

- Based on Debian 6 "Squeeze" (2014-10-30)

- Debian Qt5

- Based on Debian 8 "Jessie" + Qt5.9.1 (2017-10-06)

Remark: It must be used with i.MX6 Vendor Kernel 4.1.15

- Based on Debian 8 "Jessie" + Qt5.9.1 (2017-10-06)

- Based on Debian 8 "Jessie" + Qt5.7.1 (2016-12-19)

Remark: It must be used with i.MX6 Vendor Kernel 3.10.17

- Based on Debian 8 "Jessie" + Qt5.7.1 (2016-12-19)

Virtual Machine for Application Development

- Debian 8 "Jessie" VMware Image

Password for devel user: devel

Password for root user: root

- Debian 6 "Squeeze" VMware Image (PW: dhelectronics)

Password for devel user: devel

Password for root user: root

Mainline Linux 4.4.x eMMC update package

- i.MX6 Linux Kernel 4.4.60 with Debian Jessie Rootfilesystem

Extract files to USB stick and use stick to update i.MX6 Solo, DualLite or Quad

Code Examples for Userspace-Applications to Access SPI, I2C, GPIOs, and more

- Download Code Examples SPI, I2C, GPIOs, RTC, UART, Watchdog, and more

- Download C++ HAL class library for SPI, I2C, GPIO, UART and physical address space access

WEC7 DHHalLib.dll (function library)

- Download DHHalLib Library Version 1.3.0.0

- DHHalLib Demo App Source Code

- DHHalLib Demo App Binary File

- Download DHHalLib CSharp Demo Wrapper App

- Download DHHalLib CSharp Demo Wrapper App Binary File